⚙️STM32 DAC 性能释放

引入

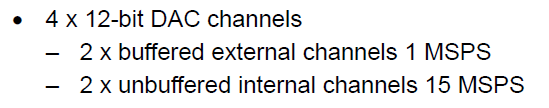

最近研究STM32G4系列的时候,在手册里看到了如下内容。

图中提到的 unbuffered channels 居然能实现 15MSPS 的DAC采样率。也就是说如果以15个点描绘周期,STM32的内嵌DAC就能突破 1MHz 的大关。

不过这样其实没什么实际意义,15个点对于绝大多数波形而言都是不够用的。而且仔细一看,这里还有个 internal 的限定,也就是说,只有DAC内部通道才能用这么高的采样率。

虽然白高兴了一场,但在搜集资料的途中,倒还真让我找到了一种提升DAC输出性能的办法:通过禁用内部 buffer ,并在引脚上外接高性能运放,可以完全解放DAC的性能上限。

具体可以参考下面这篇来自ST官方的文章:

Extending the DAC performance of STM32 microcontrollers

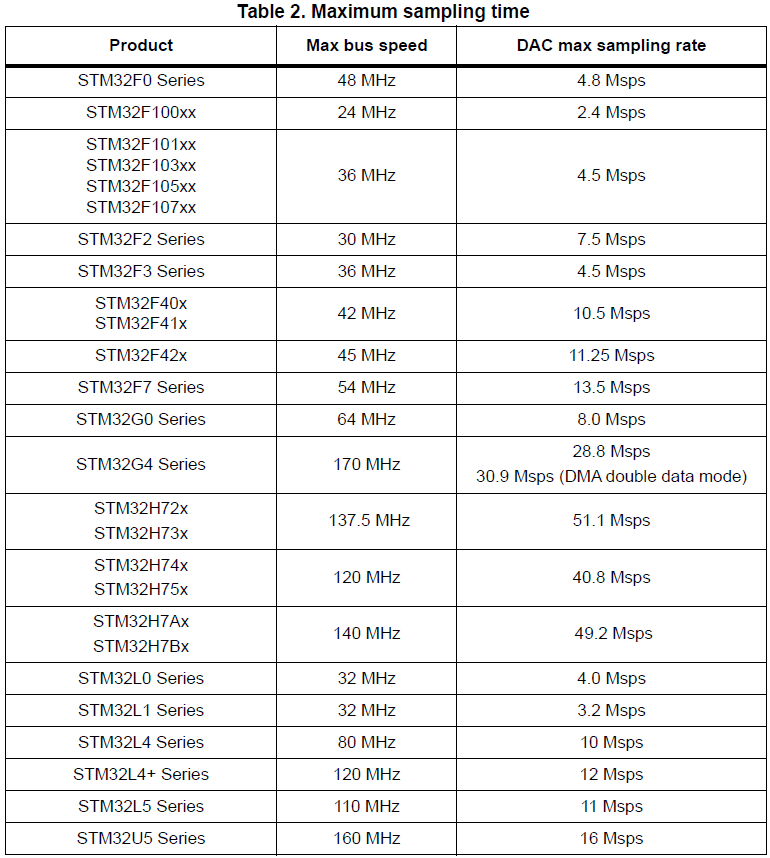

以及这张表中的数据:

分析

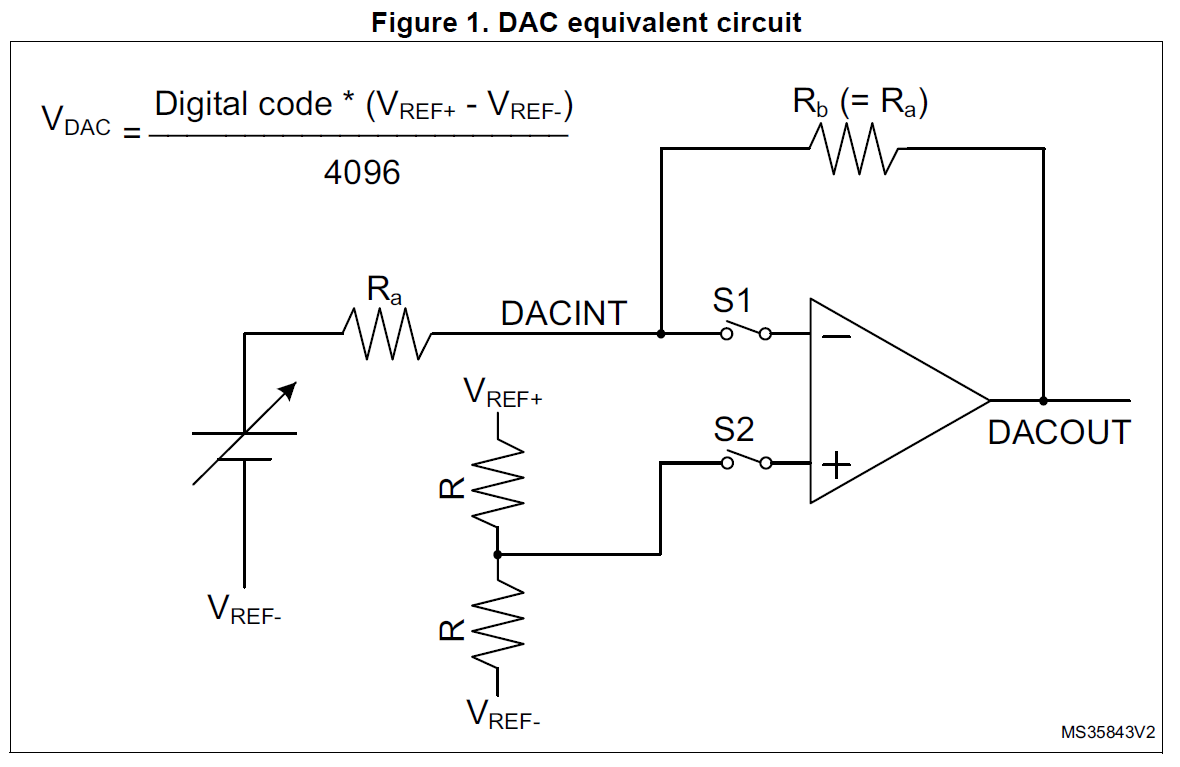

DAC等效电路

首先,我们先来看看STM32的DAC等效模型。

在芯片内部的电路中,DAC的输出端结构实际上是一个反相跟随器。

当选择 Output Buffer ON (输出缓冲开启)

S1,S2闭合,那么电流会经过内部运放的反相跟随输出,此时的放大增益为 $A_v = -1$

当选择输出缓冲的时,输出频率的速度就取决于内部运放的性能,也就是手册中标称的$1MHz$当选择 Output Buffer OFF (输出缓冲关闭)

S1,S2断开,电流直接经过 $R_a$ 和 $R_b$ 输出到外部引脚。

若是不使用输出缓冲,那么DAC的输出端就是纯阻性。而外接的负载如果具有容性,那么就会构成RC回路,造成输出频率的进一步下降。

关于输出缓冲关闭的情况下,以文中提到的以STM32F407为例,在最大阻值为$15k\Omega$,容性负载$10pF$的情况下,求得DAC的 settling time 仅有$1.8\mu s$左右,即$555kHZ$

这让本就不高的DAC输出速率雪上加霜😖

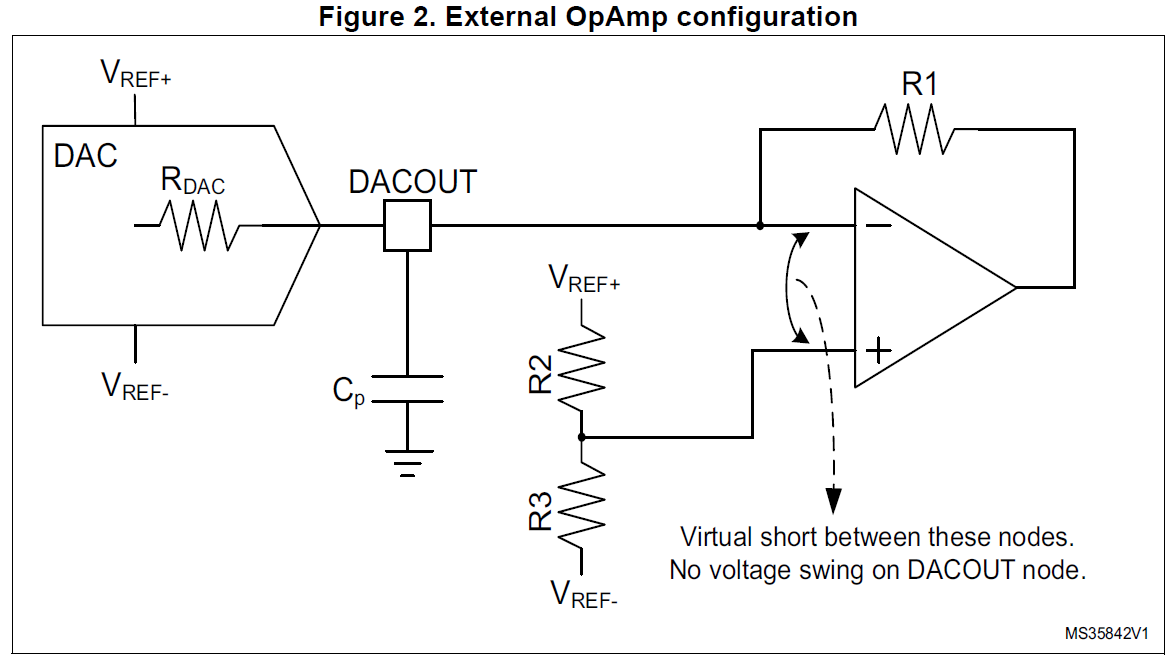

外部运放的实现

前面提到了外部容性对于STM32的DAC输出影响,若我们在引脚上额外连接一个运放,那么就能忽视 DACOUT capacitance,也就是DAC输出的容性负载,以及其带来的负面影响。

其次如果这个外接运放的性能足够高,那么就足以支持更高采样率的DAC信号输出。不过这里的反馈电阻$R_1$需要与内部的$R_{DAC}$相等,这样才能得到正确的增益大小。

DMA双重数据模式

除此之外,这里还有个需要额外注意的小特性。部分STM32芯片支持所谓的 Double Data Mode ,例如G4系列。这个模式允许每次DMA传输两组数据,将两组数据分别存储在前后16bit上,共同组成32bit的数据,一次性传输,这样就能提升DMA的带宽利用率。

不过根据文章提供的DAC极限采样率表所展示的,实际带来的DAC输出频率提升并不是很多,各位读者手中的芯片如果不支持这个功能也无妨,表中只有 G4 Series 做了这项测试,提升也很有限。

实践

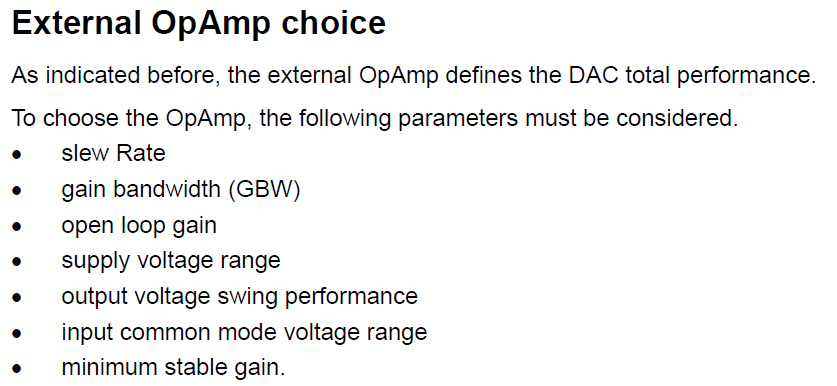

外部运放的选型

选择运放的时候应当参考上述图片中提到的参数,这里仅仅提一下其中最重要的两个参数:

slew Rate

压摆率,指的是输出信号在高低变化时,电压的最大变化速率,通常以$V/\mu s$表示。如果压摆率跟不上实际电压变换速率,就会出现一定程度的失真。在具体计算时可以参考如下公式:$$ Slew Rate \ge 2 * \pi * f * V_p$$

其中$f$为最高信号频率,$V_p$为最大峰值电压。

gain bandwidth (GBW)

增益带宽积,通常以kHZ或者MHz为单位。由于这里选择将运放作为电压跟随器,所以只要 GBW 能大于最终的输出频率即可。不过官方文章推荐至少高出两倍最好。

不过最终的DAC输出速率并不完全取决于外接运放,还与STM32芯片本身的输出性能息息相关,建议参考前文中提到的性能表格。

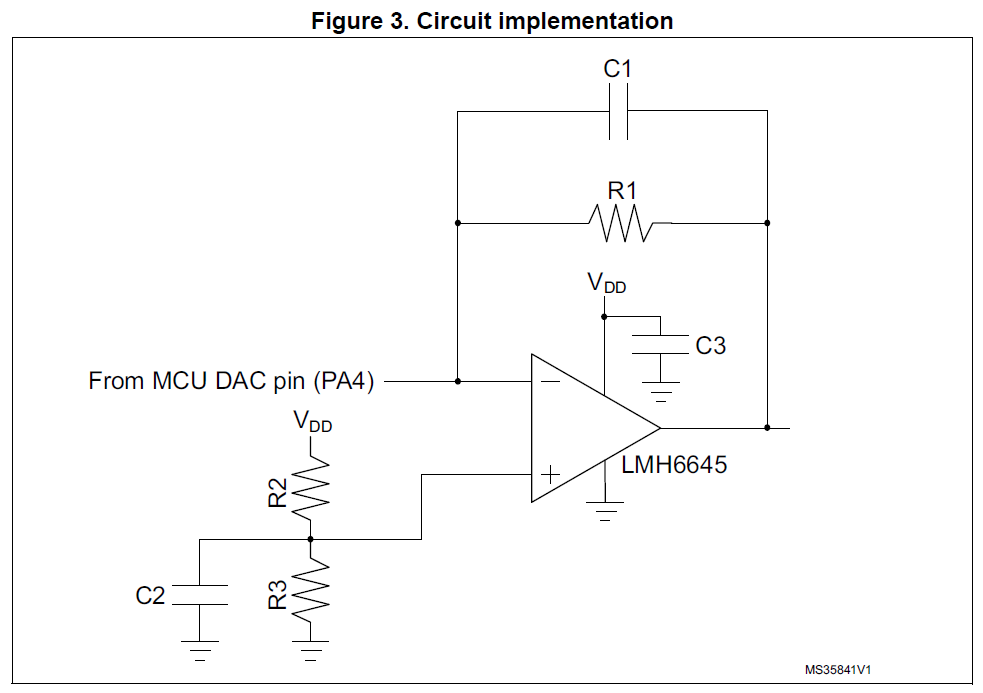

硬件电路的实践

官方文章的最后,提供了一套实际的参考方案。

案例中选用的运放 LMH6645 具体性能参数如下,可供参考。

- slew rate: 22 V/μs

- gain band width: 55 MHz

- open loop gain: 87 dB

- supply voltage range: 2.5 to 12 V

- input common mode voltage 0.3 V beyond rails

- output voltage swing 20 mV from rails

- stable from gain +1

其中出现在反馈回路上的电容C1是用于避免电压过冲,而其他部分均与先前理论分析中的外接电路保持一致,不再一一解释。

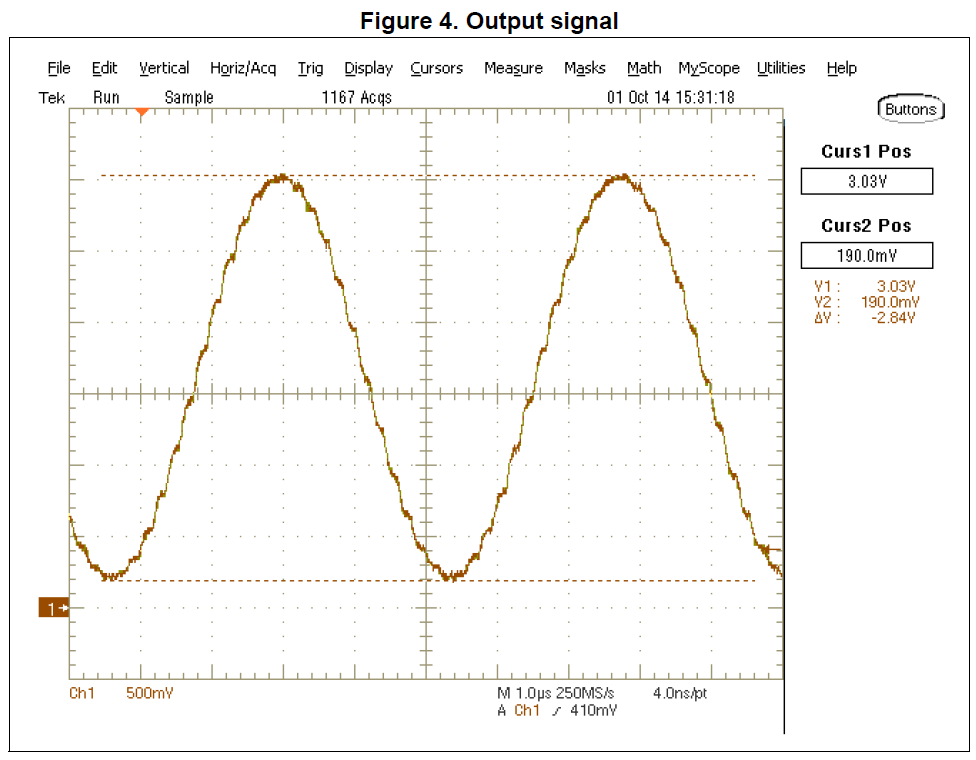

最终测试证明当输出5MSPS、3Vpp的正弦波时无明显失真,不过阶梯效应仍有点影响波形美观,可以考虑低通滤除。

复现

笔者在经过复现验证发现,确实有一定的提高效果,但与理论数据还是有些差距。

首先是复现条件:

- 主控芯片:

STM32G431CBU6 - 运放:

AD8031

在测试过程中,将正弦波输出频率从小到大逐次增加,直到 200KHz 左右仍能保持良好波形,再高就会出现波形失真和频率不稳定,甚至直接停止输出。由此可见这种做法确实有一定的提高效果,但受限于各方面因素,这样的提升并不是那么划算。

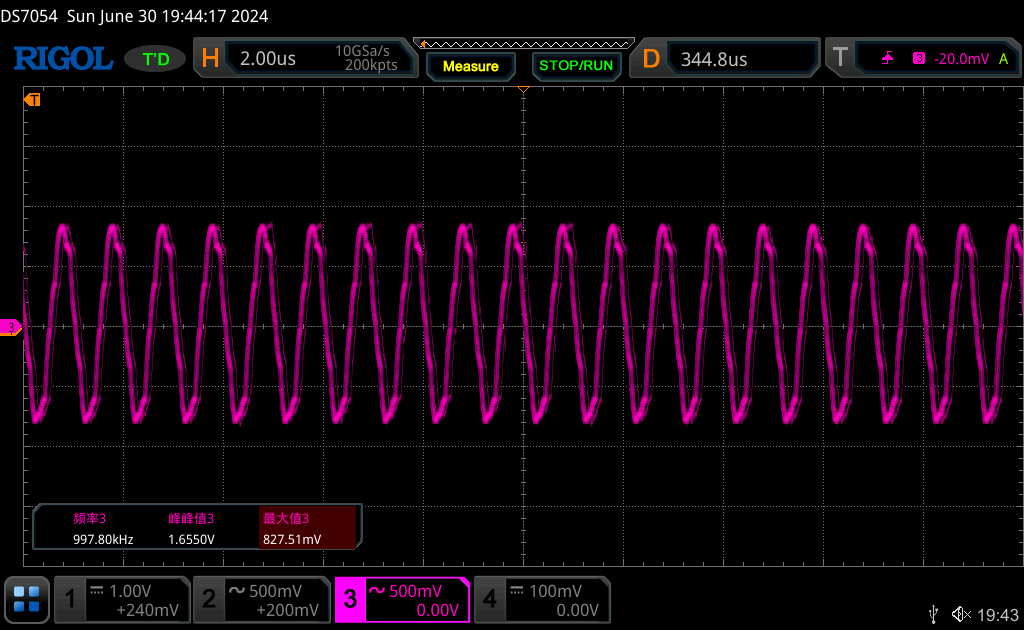

以下是本次测试最高频率的结果:

确实登上了 1MHz 的大关,笔者本人对此结果还算满意,本篇博客至此可以告一段落了。

需要注意的是,初次测量不要忘记放大器的拓扑结构是反相放大,因此好像会出现抬压一样的效果。其实这是正常现象,所谓的抬压其实是波形被倒置过来了,输出后级采用交流耦合即可。

原文中还有相当多的小细节笔者并未提到,推荐自行阅读原文😀